谘詢電話

ENGLISH0755-88840386基於FPGA的電子稱重儀設計

發布時間:2021-06-11 15:30:46 |來源:網絡轉載

0引言

稱重儀(衡器)是重量計量器具,廣泛用於工業、交通、商貿等領域,其測量精度和速度直接影響管理部門決策及物資貿易結算效率。隨著電子技術的發展,電子稱重儀以其測量精度高、速度快、信號便於計算機控製等優點逐漸取代傳統機械式稱重儀。

FPGA(現場可編程門陣列)具有高集成性、低功耗、內部延時小、隨著FPGA在高速數據采集方麵的優勢,本文設計了一款基於FPGA的多路采集電子稱重儀,以EPF10K10LC84-4為控製核心,實時采集8路稱重數據按通道順序依次顯示於液晶顯示屏,並通過RS232串口通信模塊發送至上位機。該係統結構簡單、工作可靠,功能易擴展,滿足實際工程需求。

1係統組成及工作原理

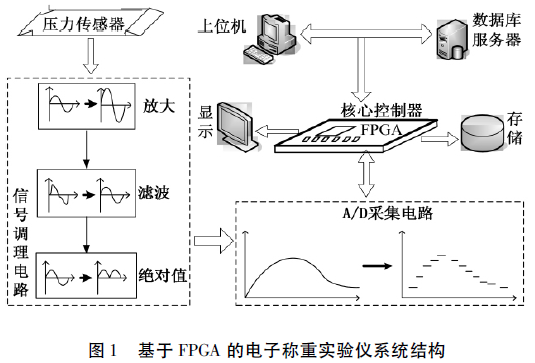

基於FPGA的電子稱重儀主要由信號調理電路、A/D采集電路、核心控製器、顯示和通訊電路組成,係統結構如圖1所示。

稱重時,傳感器內電阻應變片(基體)受到形變使惠斯通電橋失去平衡,輸出級差分電壓。為提高A/D采集精度,需將此信號經過放大、濾波、絕對值轉換等調理電路後接入A/D轉換芯片MAX1312。核心控製器FPGA根據MAX1312工作時序完成8路稱重數據采集,並完成稱重數據存儲、液晶屏顯示和串行通訊。

2係統硬件設計

2.1稱重傳感器

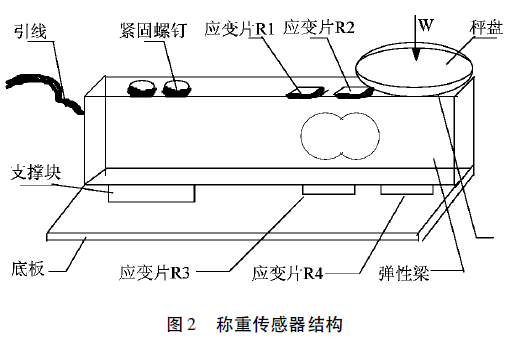

稱重傳感器利用應變測力原理,通過彈性元件將力以形變的形式傳遞給應變片。本係統采用型號為LHD001的電壓型壓力傳感器,靈敏度為2mV/V,供電電壓為6V~15V,稱重傳感器結構圖如圖2所示[1]。其中引線4根:紅色接+5V、綠色為正向輸出IN+、白色為反向輸出信號IN-、黑色接地。

2.2信號調理電路

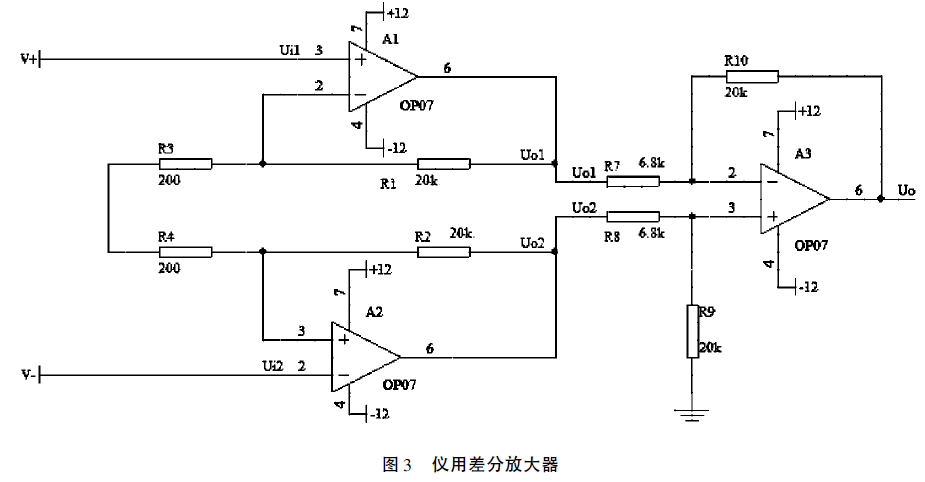

稱重傳感器靈敏度用於估計A/D轉換的輸入電壓和觸發門檻電壓[2]。因LHD001型壓力傳感器靈敏度為2mV/V,供電電壓為6V時,輸出電壓不超過12mV。為了與(ADC)MAX13120.3V~5.3V輸入電壓範圍相匹配,需對傳感器輸出信號進行放大調理。放大倍數選取時通常要考慮A/D轉換輸入模擬信號電壓在A/D輸入電壓滿量程左右,即取值277.8左右。選用3片高共模抑製比(CMRR)、低溫漂的OP07組成一個儀用差分放大器,電路圖如圖3所示。

圖3中,A1和A2形成一級放大,A3形成二級放大,

R1=R2=20kΩ,R3=R4=200Ω,R7=R8=6.8kΩ,

R9=R10=20kΩ,則放大倍數為:297.06

模擬信號放大的同時內部高頻噪音也得到放大,為此采用壓控電壓源型二階有源低通濾波電路濾除高頻噪音。傳感器輸出的模擬信號經儀用放大器反向放大,再經過低通濾波,此時信號為負值,故采用絕對值電路將此信號轉化為正值輸出。

2.3A/D采集模塊

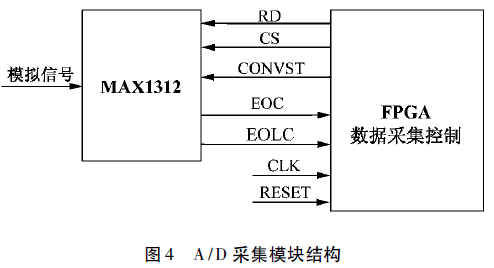

係統采用Maxim公司12位模數轉換器(ADC)MAX1312完成模數轉換。MAX1312能提供8個、4個或2個獨立輸入通道,各通道具有獨立采樣保持(T/H)電路,可支持同時采樣。8通道同時轉換時間僅需1.98μs,每個通道吞吐率為456ksps。FPGA芯片選用ALTERA公司生產的EPF10K10LC84-4,采用可重構的CMOSSRAM工藝,內嵌功能模塊豐富。A/D采集模塊結構圖如圖4所示。

圖4中,模擬信號從MAX1312的CH0~CH7輸入,FPGA內采樣控製器根據MAX1312工作時序將模擬量轉換成12位數字量D0~D11傳送至FPGA內存儲器進行數據處理。

2.4LCM液晶顯示模塊

LCM液晶顯示模塊由LCD控製器、LCD驅動器、LCD顯示裝置三部分組成。其中,LCD控製器用於與FPGA芯片進行溝通,LCD驅動器負責點亮LCD顯示裝置。本係統采用的LCM模塊是將LCD控製器、LCD驅動器集成到一塊IC芯片,型號為HD44780。

2.5通信電路

FPGA通過RS232與上位機進行通訊。本設計使用9針接口中2、3、5三個管腳進行通信。由於FPGA是使用3.3V係統,而RS232信號使用負邏輯,邏輯0電壓範圍是+5V~+15V,而邏輯1的電壓範圍是-15V~-5V,所以使用SP3232E進行

RS232電平轉換[4]。

3係統軟件設計

3.1采樣控製器

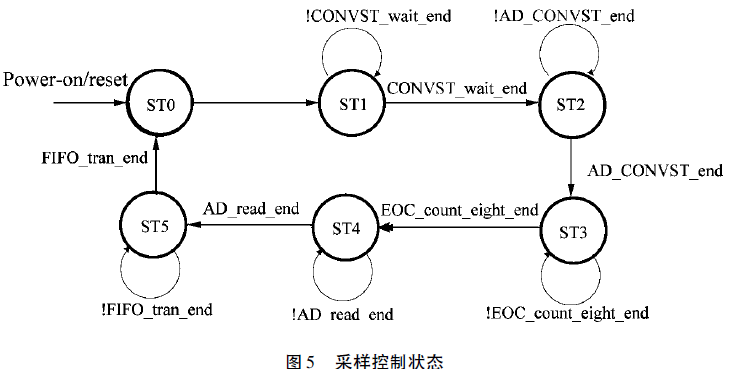

首先配置寄存器,選擇需要轉換的A/D通道。然後通過CONVST發出開始轉換信號,八個通道開始轉換。AD1_EOC_in用於計數,計滿8次後表示8個通道數據采集完成,此時AD1_EOLC_in轉為低電平。EOLC為8信號通道數據采集完成標誌,EOLC跳變到低電平表明最後一個通道轉換借宿,此時將數據存入FIFO,結束數據采集並進入新循環。圖5是MAX1312采樣控製狀態圖。

係統上電或重啟後進入狀態ST0,實現A/D參數初始化,並保持一段時延;FPGA對CONVST產生觸發信號(上升沿)啟動A/D轉換,進入狀態ST1,否則繼續保持ST0EOC是A/D轉換結束1次的標

誌ST2狀態中采用計數器對EOC下降沿計數當計滿8後表示通道轉換結束,進入狀態ST3;ST3中,通過檢測進程中的AD_convst_end信號結束判斷是否讀取轉換後的數據;狀態ST4是將8通道A/D采集的數據發送至FIFO;狀態ST5是將讀取到的數據傳送至SLAVEFIFO;數據存儲完成後,FIFO_tran_end置有效信號,轉變到初始狀態,完成對A/D的采集與傳輸。

3.2LCD顯示模塊

3.2.1譯碼模塊設計

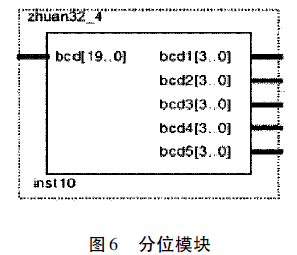

為了能在LCD模塊上正常顯示,A/D轉換後的二進製數據需先轉換為BCD碼並移位送給LCM模塊。將十二位數據輸入後左移一位,檢測個、十、百位是否滿5,滿5則對該位數加3並向左移動一位,再進行如上檢測,直至轉換為20位BCD碼。定義五個四位總線類型的寄存器變量,將20位BCD碼從低到高四位一組依次賦給寄存器變量,並從bcd1、bcd2、bcd3、bcd4、bcd5端口輸出,分位模塊如圖6所示。

3.2.2稱重顯示模塊設計

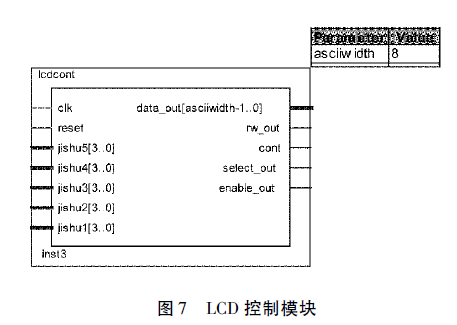

FPGA按時序驅動LCD:首先預熱LCD(全0指令)進行功能設置;設置顯示狀態、屏幕畫麵移動方式和光標移動方式,然後清除顯示畫麵;設置顯示模式(設置幾行顯示);最後打開畫麵進入數據采集流程。輸入地址選擇LCD顯示位置,然後將需要顯示的數據與ASCⅡ碼表進行對照,譯碼輸出。LCD控製模塊如圖7所示。

其中,shuju5~shuju1為五位數字的每位BCD碼輸入端。Cont端接入地址計數信號,每來1個cont脈衝輸出1個數據,先輸出字符串‘Weight:’,然後將jishu5~jishu1輸入的數值依次顯示,在第三位的時候插入小數點,抵消前麵數值擴大倍數1000倍。Select_out信號用於選擇輸出的十二位二進製數是指令還是數值。Enable直接提供反時鍾信號進行使能控製。Rw_out信號控製讀寫模式,此處設為0,用於寫信號。

3.3係統通訊模塊

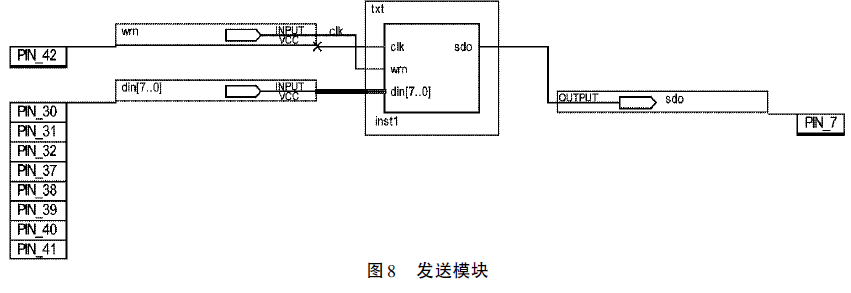

因同時采集8通道稱重數據,係統通訊模塊傳輸數據量大。為提高通信速度,采用同步通信方式,即通過同步字符在每個數據塊傳送開始時間使收發雙方同步。基於UART協議發送模塊如圖8所示。

圖中,clk為50MHz係統時鍾,Wm為發送使能端,din[7..0]接轉碼模塊處理完的數據,sdo接PC機。讀入一組8位串行數據din[7..0]到內部寄存器,從最低位開始一位一位輸出,每一位輸出後8位數據向右移一位,最高位補0,實現數據串行發送。

4係統標定

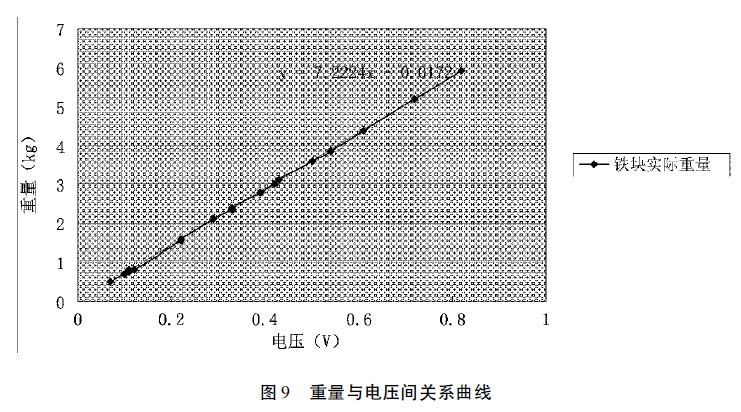

實驗采用8個重量分別為0.710kg、0.820kg、0.745kg、0.795kg、0.765kg、0.770kg、0.515kg、0.785kg的鐵塊作為實驗待測樣本,待測鐵塊從同一通道輸入,測得稱重重量與模擬信號經放大反向後輸出電壓間數據,並用最小二乘法曲線擬合後如圖9所示。

圖9觀測到傳感器壓力信號與轉變後電信號間為線性關係,用最小二乘法線性擬合後關係式為y=7.222(x-0.0024),其中x為電壓值,單位V;y為重量,單位kg;7.222為標定係數;0.0024為零點電壓值。

5結束語

實驗測試表明:所設計開發的基於FPGA的電子稱重儀性能可靠、操作簡單、測量精度較高,同時利用FPGA高集成性、I/O口多的優勢,容易滿足功能擴展和係統升級要求,具有很高的實用價值。

本文源於網絡轉載,如有侵權,請聯係刪除

- 上一篇:定量包裝秤的選擇

- 下一篇:基於GPS及GPRS技術的大噸位稱重儀